Cs Go Bind Slot 3

The final part of this bind, 'bind 4 'slot8; clcrosshairsize 1000', firstly binds the 4 key to slot8 (nade slot) and secondly binds the 'clcrosshairsize 1000' command to the 4 key, which makes your crosshair big so that you can use it to line up smokes and nades.

-->Here’s how to add jump throw bind in CS:GO. Only a small part of the players can perfectly match the throw of a grenade with a jump. Manual execution of this action requires perfect timing, no lag and a lot of practice. So I got a new mouse, the Logitech G502. I want to Bind Primary weapon to Mouse 5, Knife to Mouse 4 and Secondary to Mouse 3. My problem is in the settings page I cannot press the key to bind to each mouse key. I want to try binding the keys manually in Console. Please help a grill in need!!!! ゚・ ヾ╲(。 ‿ 。)╱ ・゚.

This topic describes some specific features of using High Level Shader Language (HLSL) Shader Model 5.1 with Direct3D 12. All Direct3D 12 hardware supports Shader Model 5.1, so support for this model does not depend on what the hardware feature level is.

Resource types and arrays

Shader Model 5 (SM5.0) resource syntax uses the register keyword to relay important information about the resource to the HLSL compiler. For example, the following statement declares an array of four textures bound at slots t3, t4, t5, and t6. t3 is the only register slot appearing in the statement, simply being the first in the array of four.

Shader Model 5.1 (SM5.1) resource syntax in HLSL is based on existing register resource syntax, to allow easier porting. Direct3D 12 resources in HLSL are bound to virtual registers within logical register spaces:

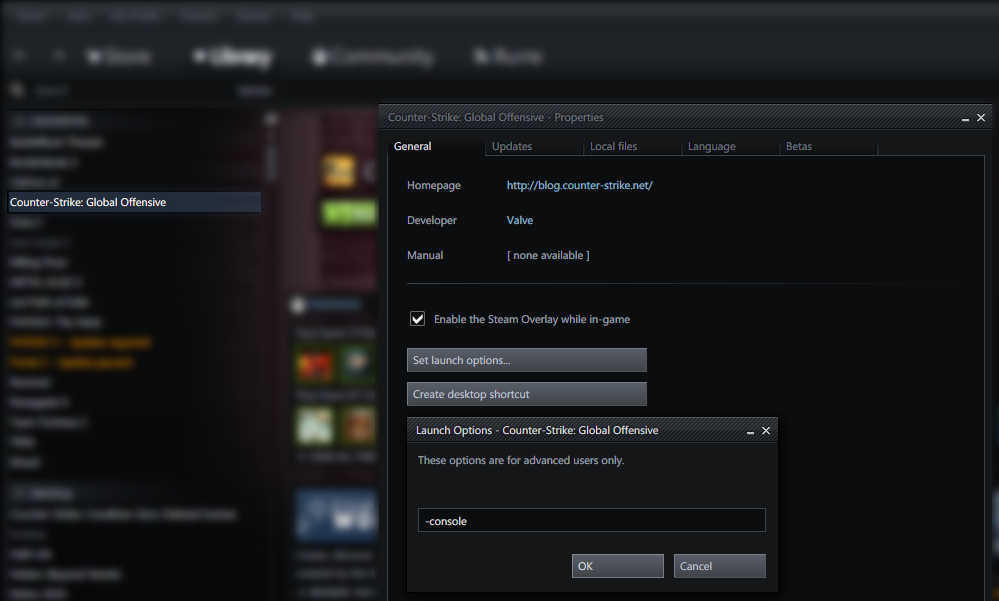

- Activating the bind If you have downloaded it from my dropbox simply paste it in C: Program Files (x86) Steam steamapps common Counter-Strike Global Offensive csgo cfg If not go to the same place and create a text document. Paste the bind into that and then save it as a.cfg file. Once this is done enter the game.

- For example, the following statement declares an array of four textures bound at slots t3, t4, t5, and t6. T3 is the only register slot appearing in the statement, simply being the first in the array of four. Texture2D tex14: register(t3).

- t – for shader resource views (SRV)

- s – for samplers

- u – for unordered access views (UAV)

- b – for constant buffer views (CBV)

The root signature referencing the shader must be compatible with the declared register slots. For example, the following portion of a root signature would be compatible with the use of texture slots t3 through t6, as it describes a descriptor table with slots t0 through t98.

A resource declaration may be a scalar, a 1D array, or a multidimensional array:

SM5.1 uses the same resource types and element types as SM5.0 does. SM5.1 declaration limits are more flexible, and constrained only by the runtime/hardware limits. The space keyword specifies to which logical register space the declared variable is bound. If the space keyword is omitted, then the default space index of 0 is implicitly assigned to the range (so the tex2 range above resides in space0). register(t3, space0) will never conflict with register(t3, space1), nor with any array in another space that might include t3.

An array resource may have an unbounded size, which is declared by specifying the very first dimension to be empty, or 0:

The matching descriptor table could be:

An unbounded array in HLSL does match a fixed number set with numDescriptors in the descriptor table, and a fixed size in the HLSL does match an unbounded declaration in the descriptor table.

Multi-dimensional arrays are allowed, including of an unbounded size. These multidimensional arrays are flattened out in register space.

Aliasing of resource ranges is not allowed. In other words, for each resource type (t, s, u, b), declared register ranges mustn't overlap. That includes unbounded ranges, too. Ranges declared in different register spaces never overlap. Note that unbounded tex2 (above) resides in space0, while unbounded tex3 resides in space1, such that they don't overlap.

Accessing resources that have been declared as arrays is as simple as indexing them.

There's an important default restriction on the use of the indices (myMaterialID and samplerID in the code above) in that they're not allowed to vary within a wave. Even changing the index based on instancing counts as varying.

If varying the index is required then specify the NonUniformResourceIndex qualifier on the index, for example:

On some hardware the use of this qualifier generates additional code to enforce correctness (including across threads) but at a minor performance cost. If an index is changed without this qualifier and within a draw/dispatch the results are undefined.

Descriptor arrays and texture arrays

Texture arrays have been available since DirectX 10. Texture arrays require one descriptor, however all the array slices must share the same format, width, height and mip count. Also, the array must occupy a contiguous range in virtual address space. The following code shows an example of accessing a texture array from a shader.

In a texture array, the index can be varied freely, without any need for qualifiers such as NonUniformResourceIndex.

The equivalent descriptor array would be:

Note the awkward use of a float for the array index is replaced with myTex2D[2]. Also descriptor arrays offer more flexibility with the dimensions. The type, Texture2D is this example, cannot vary, but the format, width, height, and mip count can all vary with each descriptor.

It is legitimate to have a descriptor array of texture arrays:

It is not legitimate to declare an array of structures, each structure containing descriptors, for example the following code is not supported.

This would have allowed the memory layout abcabcabc...., but is a language limitation and is not supported. One supported method of doing this would be as follows, though the memory layout in this case is aaa...bbb...ccc....

To achieve the abcabcabc.... memory layout, use a descriptor table without use of the myStruct structure.

Resource aliasing

The resource ranges specified in the HLSL shaders are logical ranges. They are be bound to concrete heap ranges at runtime via the root signature mechanism. Normally, a logical range maps to a heap range that does not overlap with other heap ranges. However, the root signature mechanism makes it possible to alias (overlap) heap ranges of compatible types. For example, tex2 and tex3 ranges from the above example may be mapped to the same (or overlapping) heap range, which has the effect of aliasing textures in the HLSL program. If such aliasing is desired, the shader must be compiled with D3D10_SHADER_RESOURCES_MAY_ALIAS option, which is set by using the /res_may_alias option for the Effect-Compiler Tool (FXC). The option makes the compiler produce correct code by preventing certain load/store optimizations under the assumption that resources may alias.

Divergence and derivatives

SM5.1 does not impose limitations on the resource index; i.e., tex2[idx].Sample(…) – the index idx can be a literal constant, a cbuffer constant, or an interpolated value. While the programming model provides such great flexibility, there are issues to be aware of:

- If index diverges across a quad, the hardware-computed derivative and derived quantities such as LOD may be undefined. The HLSL compiler makes the best effort to issue a warning in this case, but will not prevent a shader from compiling. This behavior is similar to computing derivatives in divergent control flow.

- If the resource index is divergent, the performance is diminished compared to the case of a uniform index, because the hardware needs to perform operations on several resources. Resource indexes that may be divergent must be marked with the

NonUniformResourceIndexfunction in HLSL code. Otherwise results are undefined.

UAVs in pixel shaders

SM5.1 does not impose constraints on UAV ranges in pixel shaders as was the case for SM5.0.

Constant Buffers

SM5.1 constant buffers (cbuffer) syntax has changed from SM5.0 to enable developers to index constant buffers. To enable indexable constant buffers, SM5.1 introduces the ConstantBuffer “template” construct:

The preceding code declares constant buffer variable myCB1 of type Foo and size 6, and a scalar, constant buffer variable myCB2. A constant buffer variable can now be indexed in the shader as:

Fields ‘a’ and ‘b’ do not become global variables, but rather must be treated as fields. For backward compatibility, SM5.1 supports the old cbuffer concept for scalar cbuffers. The following statement makes ‘a’ and ‘b’ global, read-only variables as in SM5.0. However, such an old-style cbuffer cannot be indexable.

Currently, the shader compiler supports the ConstantBuffer template for user-defined structures only.

For compatibility reasons, the HLSL compiler may automatically assign resource registers for ranges declared in space0. If ‘space’ is omitted in the register clause, the default space0 is used. The compiler uses the first-hole-fits heuristic to assign the registers. The assignment can be retrieved via the reflection API, which has been extended to add the Space field for space, while the BindPoint field indicates the lower bound of the resource register range.

Bytecode changes in SM5.1

SM5.1 changes how resource registers are declared and referenced in instructions. The syntax involves declaring a register “variable”, similar to how it is done for group shared memory registers:

This will disassemble to:

Each shader resource range now has an ID (a name) that is unique to the shader bytecode. For example, tex1 (t10) texture array becomes ‘T1’ in the shader bytecode. Giving unique IDs to each resource range allows two things:

- Unambiguously identify which resource range (see dcl_resource_texture2d) is being indexed in an instruction (see sample instruction).

- Attaching a set of attributes to the declaration, e.g., element type, stride size, raster operation mode, etc.

Note that the ID of the range is not related to the HLSL lower bound declaration.

The order of reflection resource bindings (listing at the top) and shader declaration instructions (dcl_*) is the same to aid in identifying the correspondence between HLSL variables and bytecode IDs.

Cs Go Bind Slot 3.0

Each declaration instruction in SM5.1 uses a 3D operand to define: range ID, lower and upper bounds. An additional token is emitted to specify the register space. Other tokens may be emitted as well to convey additional properties of the range, e.g., cbuffer or structured buffer declaration instruction emits the size of the cbuffer or structure. The exact details of encoding can be found in d3d12TokenizedProgramFormat.h and D3D10ShaderBinary::CShaderCodeParser.

SM5.1 instructions will not emit additional resource operand information as part of the instruction (as in SM5.0). This information is now in the declaration instructions. In SM5.0, instructions indexing resources required resource attributes to be described in extended opcode tokens, since indexing obfuscated the association to the declaration. In SM5.1, each ID (such as ‘t1’) is unambiguously associated with a single declaration that describes the required resource information. Therefore, the extended opcode tokens used on instructions to describe resource information are no longer emitted.

In non-declaration instructions, a resource operand for samplers, SRVs, and UAVs is a 2D operand. The first index is a literal constant that specifies the range ID. The second index represents the linearized value of the index. The value is computed relative to the beginning of the corresponding register space (not relative to the beginning of the logical range) to better correlate with the root signature and to reduce the driver compiler burden of adjusting the index.

A resource operand for CBVs is a 3D operand, containing: literal ID of the range, index of the constant buffer, offset into the particular instance of constant buffer.

Example HLSL Declarations

HLSL programs do not need to know anything about root signatures. They can assign bindings to the virtual “register” binding space, t# for SRVs, u# for UAVs, b# for CBVs, s# for samplers, or rely on the compiler to pick assignments (and query the resulting mappings using shader reflection afterwards). The root signature maps descriptor tables, root descriptors, and root constants to this virtual register space.

The following are some example declarations an HLSL shader might have. Note that there are no references to root signatures or descriptor tables.

Related topics

Bind Commands

The command for the most popular variation of this bind is below. When you press 4, the nade lineup crosshair will be activated - to change this key, press the 'Change Key' button. Pressing 1, 2, or 3, will revert to your normal crosshair size. You will need to change cl_crosshairsize 3 to your own crosshair size. Copy and paste this command into your console to apply bind.

How it Works

The above 'command' is actually made up of four different commands.

The first command, 'bind 1 'slot1 ; cl_crosshairsize 3';' binds the 1 key to two commands: the 'cl_crosshairsize 3' command which will set your crosshair size back to 3, so that your crosshair will return to normal (change 3 to whatever your usual crosshair size is). Also, because we don't want to override the default setting for the 1 key (switching to your primary weapon), this command also binds 1 to 'slot1', which will switch to your primary weapon when 1 is pressed.

The next two commands: 'bind 2 'slot2 ; cl_crosshairsize 3';' and 'bind 3 'slot3 ; cl_crosshairsize 3';' serve a similar function to the first. They will make your crosshair return to normal when you switch to your secondary weapon or knife.

Cs Go Bind Slot 3d

The final part of this bind, 'bind 4 'slot8 ; cl_crosshairsize 1000', firstly binds the 4 key to slot8 (nade slot) and secondly binds the 'cl_crosshairsize 1000' command to the 4 key, which makes your crosshair big so that you can use it to line up smokes and nades.